તેમના નવલકથા ડિઝાઇન ફ્રેમવર્કનો ઉપયોગ કરીને, ટીમે એનાલોગ ચિપસેટનો પ્રોટોટાઇપ બનાવ્યો છે જેને ARYABHAT-1 અથવા “એનાલોગ રિકોન્ફિગરેબલ ટેક્નોલોજી અને બાયસ-સ્કેલેબલ હાર્ડવેર ફોર AI કાર્યો” કહેવાય છે. સંશોધકોએ તેમના તારણોને બે પ્રી-પ્રિન્ટ અભ્યાસમાં દર્શાવ્યા છે જે હાલમાં પીઅર સમીક્ષા હેઠળ છે અને પેટન્ટ પણ ફાઇલ કરી છે.

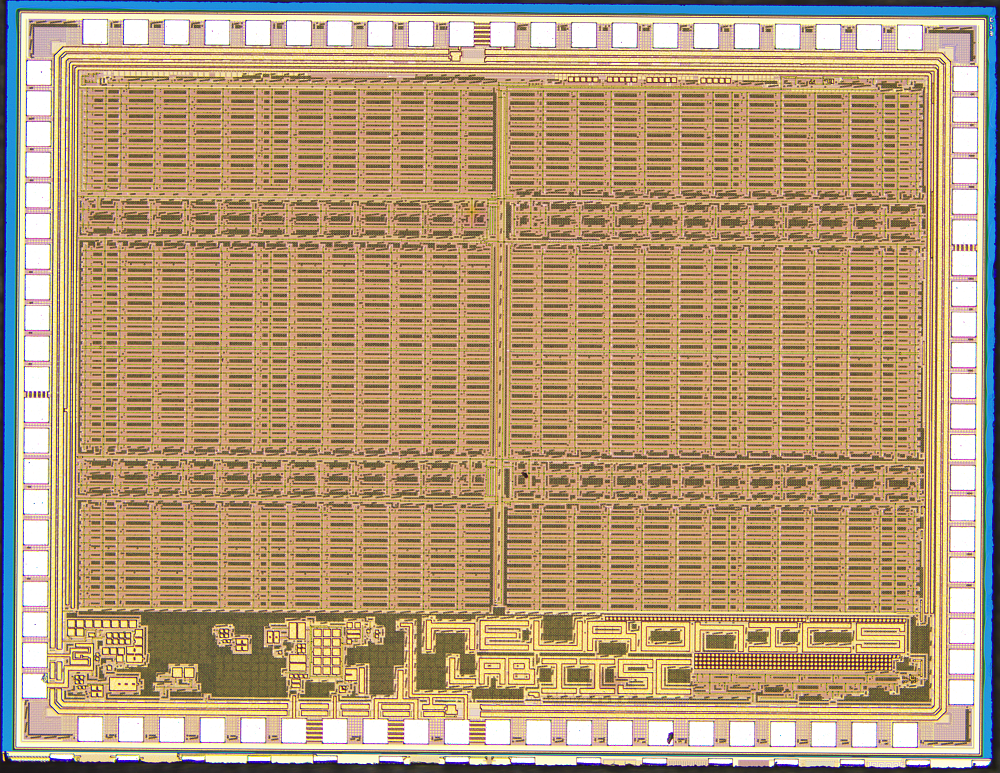

આર્યભટ-1 ચિપ માઈક્રોગ્રાફ

“આ પ્રકારનો ચિપસેટ ખાસ કરીને આર્ટિફિશિયલ ઇન્ટેલિજન્સ (AI) આધારિત એપ્લિકેશન્સ જેમ કે ઑબ્જેક્ટ અથવા સ્પીચ રેકગ્નિશન માટે મદદરૂપ થઈ શકે છે – વિચારો એલેક્સા અથવા સિરી – અથવા તે કે જેને ઉચ્ચ ઝડપે મોટા પાયે સમાંતર કમ્પ્યુટિંગ કામગીરીની જરૂર હોય છે,” IISc જણાવ્યું હતું.

મોટા ભાગના ઈલેક્ટ્રોનિક ઉપકરણો, ખાસ કરીને જેમાં કમ્પ્યુટિંગનો સમાવેશ થાય છે, તે ડિજિટલ ચિપ્સનો ઉપયોગ કેવી રીતે કરે છે તે દર્શાવે છે કારણ કે ડિઝાઇન પ્રક્રિયા સરળ અને સ્કેલેબલ છે. ચેતન સિંહ ઠાકુર, આસિસ્ટન્ટ પ્રોફેસર, ડિપાર્ટમેન્ટ ઓફ ઇલેક્ટ્રોનિક સિસ્ટમ્સ એન્જિનિયરિંગ (DESE), સમજાવ્યું: “પરંતુ એનાલોગનો ફાયદો ઘણો મોટો છે. તમને શક્તિ અને કદમાં તીવ્ર સુધારણાના ઓર્ડર મળશે.”

ઠાકુરની લેબ એનાલોગ ચિપસેટ વિકસાવવાના પ્રયાસોનું નેતૃત્વ કરી રહી છે. એપ્લીકેશનમાં કે જેને ચોક્કસ ગણતરીઓની જરૂર નથી, એનાલોગ કમ્પ્યુટિંગમાં ડિજિટલ કમ્પ્યુટિંગને પાછળ રાખવાની ક્ષમતા છે કારણ કે પહેલાની વધુ ઊર્જા-કાર્યક્ષમ છે, IISc એ જણાવ્યું હતું.

જો કે, એનાલોગ ચિપ્સ ડિઝાઇન કરતી વખતે દૂર કરવા માટે ઘણી ટેક્નોલોજી અવરોધો છે, IISc એ જણાવ્યું હતું કે, ડિજિટલ ચિપ્સથી વિપરીત, એનાલોગ પ્રોસેસર્સનું પરીક્ષણ અને સહ-ડિઝાઇન મુશ્કેલ છે. ઉચ્ચ-સ્તરના કોડને કમ્પાઇલ કરીને મોટા પાયે ડિજિટલ પ્રોસેસર્સ સરળતાથી સંશ્લેષણ કરી શકાય છે, અને સમાન ડિઝાઇનને ટેક્નોલોજી વિકાસની વિવિધ પેઢીઓમાં પોર્ટ કરી શકાય છે – કહો કે, 7nm ચિપસેટથી 3nm ચિપસેટ સુધી – ન્યૂનતમ ફેરફારો સાથે.

“કારણ કે એનાલોગ ચિપ્સ સરળતાથી માપવામાં આવતી નથી (નેક્સ્ટ જનરેશન ટેક્નોલોજી અથવા નવી એપ્લિકેશનમાં સંક્રમણ કરતી વખતે તેમને વ્યક્તિગત રીતે કસ્ટમાઇઝ કરવાની જરૂર છે) તેમની ડિઝાઇન ખર્ચાળ છે. બીજો પડકાર એ છે કે જ્યારે એનાલોગ ડિઝાઇનની વાત આવે છે ત્યારે પાવર અને એરિયા સાથે ચોકસાઇ અને ઝડપનું વેપાર કરવું સહેલું નથી,” IIScએ જણાવ્યું હતું.

ડિજિટલ ડિઝાઇનમાં, સમાન ચિપમાં લોજિક એકમો જેવા વધુ ઘટકો ઉમેરવાથી ચોકસાઇમાં વધારો થઈ શકે છે, અને તેઓ જે પાવર પર કાર્ય કરે છે તે ઉપકરણની કામગીરીને અસર કર્યા વિના ગોઠવી શકાય છે.

આ પડકારોને પહોંચી વળવા માટે, ટીમે એક નવતર માળખું તૈયાર કર્યું છે જે એનાલોગ પ્રોસેસર્સના વિકાસને મંજૂરી આપે છે જે ડિજિટલ પ્રોસેસરની જેમ જ સ્કેલ કરે છે. તેમના ચિપસેટને પુનઃરૂપરેખાંકિત અને પ્રોગ્રામ કરી શકાય છે જેથી સમાન એનાલોગ મોડ્યુલો પ્રક્રિયા ડિઝાઇનની વિવિધ પેઢીઓ અને વિવિધ એપ્લિકેશનોમાં પોર્ટ કરી શકાય.

“તમે ડિજિટલ ડિઝાઇનની જેમ જ 180nm અથવા 7nm પર સમાન પ્રકારની ચિપનું સંશ્લેષણ કરી શકો છો,” ઠાકુરે જણાવ્યું હતું કે, વિવિધ મશીન લર્નિંગ આર્કિટેક્ચરને આર્યભટ પર પ્રોગ્રામ કરી શકાય છે, અને ડિજિટલ પ્રોસેસરની જેમ, વિશાળ શ્રેણીમાં મજબૂત રીતે કાર્ય કરી શકે છે. તાપમાન

સંશોધકો ઉમેરે છે કે આર્કિટેક્ચર “બાયસ-સ્કેલેબલ” પણ છે – જ્યારે વોલ્ટેજ અથવા વર્તમાન જેવી ઓપરેટિંગ પરિસ્થિતિઓમાં ફેરફાર કરવામાં આવે ત્યારે તેનું પ્રદર્શન સમાન રહે છે. આનો અર્થ એ છે કે સમાન ચિપસેટ ક્યાં તો અલ્ટ્રા-એનર્જી-કાર્યક્ષમ ઇન્ટરનેટ ઓફ થિંગ્સ (IoT) એપ્લિકેશન્સ માટે અથવા ઑબ્જેક્ટ શોધ જેવા હાઇ-સ્પીડ કાર્યો માટે ગોઠવી શકાય છે.

ડિઝાઇન ફ્રેમવર્ક IISc વિદ્યાર્થીના ભાગ રૂપે વિકસાવવામાં આવ્યું હતું પ્રતિક કુમારનું પીએચડી કાર્ય, અને વોશિંગ્ટન યુનિવર્સિટીના મેકકેલ્વે સ્કૂલ ઓફ એન્જિનિયરિંગના પ્રોફેસર શાંતનુ ચક્રવર્તી સાથે મળીને, જેઓ IIScમાં મેકડોનેલ એકેડેમી એમ્બેસેડર તરીકે પણ સેવા આપે છે.

ચક્રવર્તી કહે છે, “એનાલોગ બાયસ-સ્કેલેબલ કમ્પ્યુટિંગની થિયરી વાસ્તવિકતામાં અને વ્યવહારુ એપ્લિકેશન માટે પ્રગટ થતી જોવાનું સારું છે,” ચક્રવર્તી કહે છે.